在今年的光纤通信会议(OFC) 会议上,光电共封(CPO)成为芯片厂商的一大热议话题,博通、Marvell介绍了各家的采用光电共封装技术的51.2Tbps的交换机芯片,思科也展示了其CPO技术的实现可行性原理,在光电共封技术的支持下,一个交换机的新时代正在来临!这对于光电共封技术来说是一个很大的进步,也足以表明利用光来移动数据的前景确实是光明的。

这个赛道也成为了芯片巨头的新战场。

光电共封迎来大的推动力

这一波的光电共封器件很大的推动者是数据中心的公有云供应商,随着AI/ML(人工智能/机器学习)、高分辨率视频流和虚拟现实等更高带宽应用的出现,网络流量持续增长,数据中心网络承受的压力也在不断增加,诸如谷歌、Meta、亚马逊、微软或阿里巴巴等,他们每家都部署了数万台交换机,而且正在推动数据速率从100GbE向400GbE和800GbE更高速的数据链路的方向发展,这将消耗更多的电力来通过铜缆传输数据。

作为交换机的大脑——交换机芯片,在过去多年来主要有两大长期发展趋势:

- 一,大约每两年一次,交换机芯片的带宽会翻一番,这也很好的遵循了摩尔定律。

- 二,为了支持总交换机芯片带宽的增加,Serdes的速度、数量和功率也在随之增加,SerDes的速度从10 Gbit/sec增加到112 Gbit/sec,芯片周围的SerDes数量从64通道增加到51.2 Tbps一代的512通道。SerDes功率成为系统总功率的很大一部分。

当下交换机之间所采用的方案大都是可插拔的光学器件,虽然可以很容易地更换或换成更高容量的,但这也意味着在交换机芯片和光学器件接口之间有几英寸的铜,而且由于所需的电气和光学密度、热问题和功耗,当前可插拔光学器件也面临着容量难扩展的制约。于是,业界开始探索提高数据中心效率的新方法,光电共封(CPO)成为一个有利的选择!

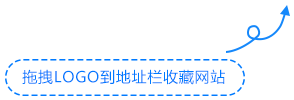

光电共封装(Co-Packaged Optics,简称CPO)是一种新型的光电子集成技术,它将光学器件(如激光器、调制器、光接收器等)封装在芯片级别上,直接与芯片内的电路相集成,借助光互连以提高通信系统的性能和功率效率。共同封装光学器件的一项关键创新是将光学器件移动到离 Switch ASIC 裸片足够近的位置,以便移除这个额外的DSP(见下图)。借助CPO,网络交换机系统中的光接口从交换机外壳前端的可插拔模块转变为与交换机芯片组装在同一封装中的光模块。

基于这种封装模式,光电共封(CPO)技术的优势尽显:

- 增强性能:CPO可以将光学元件直接嵌入芯片中,使得光学元件与芯片内部电路的距离更近,减小了电信号的延迟和失真,提高了通信系统的性能。

- 节省空间:CPO可以大大减小光模块的尺寸,尤其是在高密度数据中心环境下,可以将更多的端口装在相同大小的机柜中。

- 降低功耗:CPO可以减少能量转换的步骤,从而降低了功耗。与传统的光模块相比,CPO在相同数据传输速率下可以减少约50%的功耗。

- 提高可靠性:CPO可以提高光学和电子之间的互联可靠性,并减少外部干扰。同时,由于CPO是在芯片级别上封装的,所以也能够提高整个系统的可靠性。

- 降低成本:CPO可以减少芯片与光模块之间的连接器数量,从而降低了生产成本。此外,CPO的小尺寸和低功耗也能够降低运营成本。

正因为此,使得越来越多的芯片厂商、光通信厂商和研究机构都在积极研究和使用光电共封技术。

CPO的商业化雏形,在交换机市场中显现

博通

博通(Broadcom)涉足光电领域大约在1990年,1995年,Broadcom推出了其第一款光电收发器,这是该公司进入光电领域的开端。此后博通进行了一系列收购,1998年收购了光通信设备制造商Epigram;2000年,Broadcom收购了另一家光通信设备制造商Luminent;2016年,Broadcom收购了从事光电器件和模块研发的BroadLight。

可以说,通过不断收购,高通进一步加强了其在光电领域的研发能力,博通也开发出了电子、光学和创新封装架构 (SCIP™) 。养兵千日,如今,博通正将其在光电领域的技术积累应用到交换机产品中。

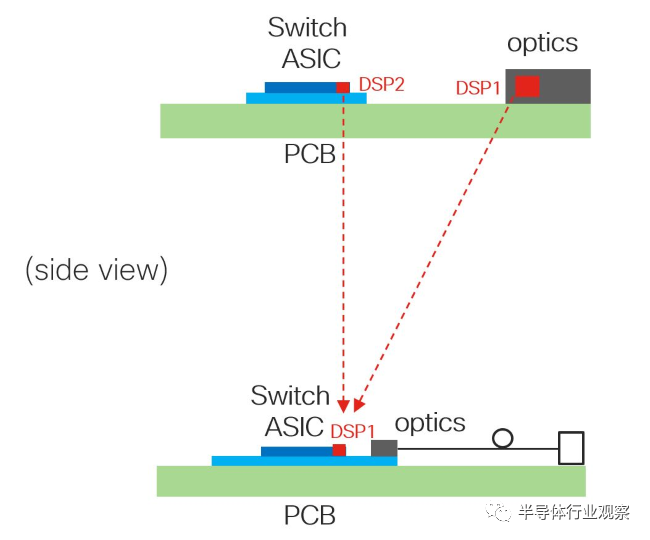

博通在2023年光纤通信会议(OFC) 上谈到了其最新的交换机产品——Broadcom Tomahawk StrataXGS 5,它在单个单片芯片中提供 51.2 Tbps 的以太网交换容量。如下图所示,该交换机值得一提的地方是,Tomahawk 5采用了光电共封装的技术,它将交换机芯片和100G PAM4接口共同封装在一起,这种新芯片能够减少将信号驱动到交换机前端的可插拔光学器件的需求,大大降低了功耗。相比于Tomahawk 4 Humboldt 25.6T6.4W的功率,该交换机仅需要5.5W的功率为800Gbps的流量供电。博通称,由于采用了光电共封(CPO)的光学技术,该芯片能将光学连接所需的功率降低50%以上。

51.2Tbps交换机中有一个新的交换芯片,这是一款5nm工艺的单片芯片,它搭载了六个Arm处理器核心,交换机上还支持VxLAN单通道以及PTP和SyncE等特性,可提供多达64个800GbE、128个400GbE、256个200GbE或512个100GbE链路。实际上,这些交换芯片是为了100GbE以上速率的交换机而设计的。博通表示,一台新的Tomahawk 5交换机可以有效地取代48台2014年代的Tomahawk 1交换机。

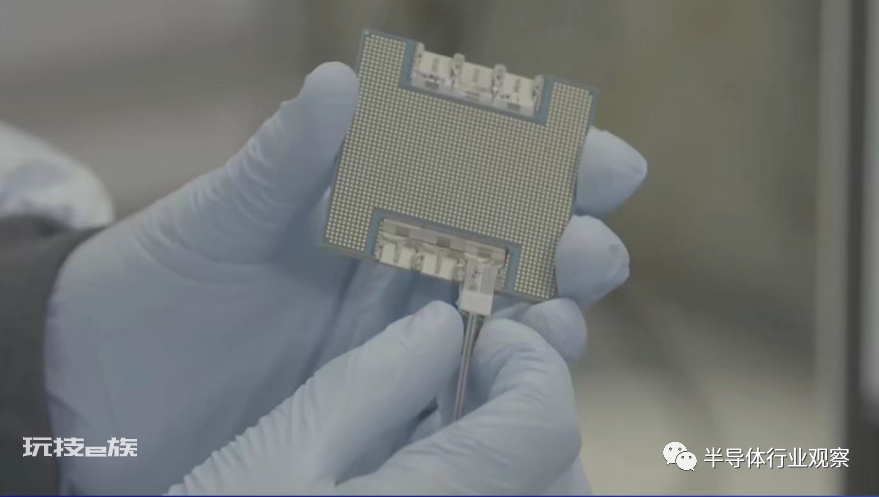

除了交换机芯片之外,博通还有光电共封的收发器产品。它也采用了博通的硅光子芯片封装 (SCIP™) 技术。

博通的光电共封收发器(图源:博通)

Marvell

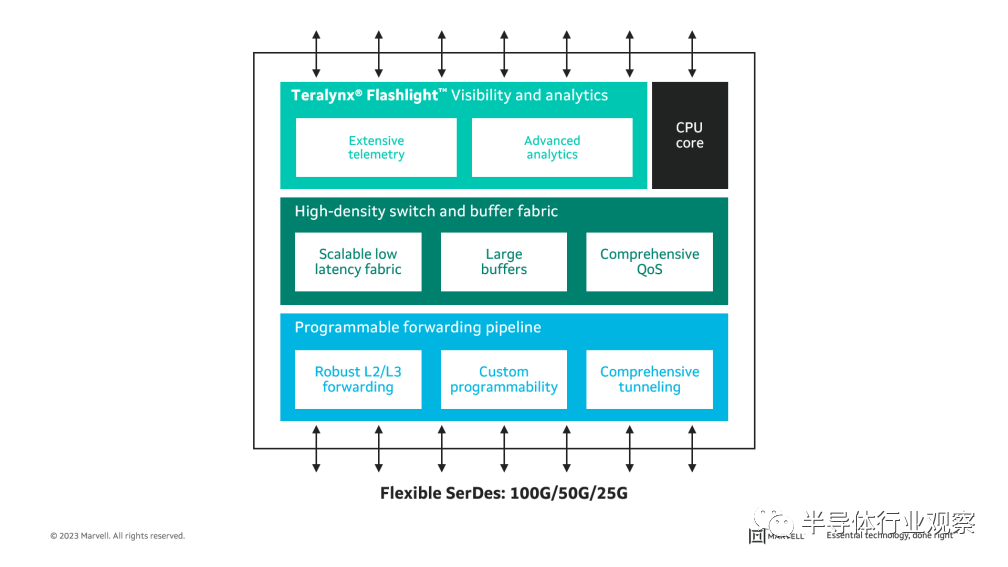

Marvell Teralynx 10交换机是另一款专为800GbE时代设计的51.2T交换机,该交换机由Marvell的Teralynx 10 51.2 Tbps交换芯片和 PAM4 1.6 Tbps 光电平台 Nova组成。Teralynx 品牌来自Marvell-Innovium的收购。

Marvell Teralynx 10芯片跟博通的一样,也是一款可编程5nm单片交换机芯片,具有512个112G SerDes,能满足32 x 1.6T、64 x 800G和128 x 400G广泛的交换机配置。按照Marvell的说法,一个Teralynx 10取代了12个12.8 Tbps一代,而且在同等容量下能减少80%的功耗。

(图源:Marvell)

Teralynx 10使用了Teralynx 独有的通用超低延迟开关和缓冲结构,还支持拥塞感知路由和实时流遥测,使网络能够自动调整和自我修复。借助线速可编程性,可以添加新的协议和功能来满足AI/ML不断变化的需求。Teralynx 10 支持广泛的实时网络遥测,包括 P4 带内网络遥测 (INT)。这些功能支持预测分析、更快的问题解决和更高程度的自动化。

(图源:Marvell)

这款新的交换机芯片可以减少AI/ML等分布式应用程序在网络上花费的时间,最大限度地提高计算利用率,并满足人工智能和机器学习不断增长的带宽需求。它适用于下一代数据中心网络中的枝叶和主干应用程序,以及 AI/ML 和高性能计算 (HPC) 结构。Teralynx 10将在第二季度提供样品。

思科

思科也在进行光电共封技术的探索,其正在和芯片制造商Inphi之间基于CPO的交换机/光学解决方案的合作,为下一代 51.2 Tb/s交换机和800 Gb/s可插拔设备开发联合封装光学器件 (CPO)。

在本次OFC 2023上,思科也演示了CPO技术实现的可行性具体步骤。思科指出,其Cisco 8111-32EH是一种传统的32端口2x400G 1RU路由器,基于Cisco Silicon One G100 ASIC的2x400G-FR4可插拔光学模块(64x400G FR4)。思科CPO路由器配备了完整的协同封装的基于硅光子学的光学tiles,驱动64x400G FR4,也基于带CPO衬底的思科Silicon One G100 ASIC。思科还发明了一种在硅光子IC上执行此复用器/解复用器的创新方法。思科预计试验部署与 51.2Tb 交换机周期同时进行,随后在 101.2Tb 交换机周期内更大规模地采用。

思科在OFC 2023 CPO演示的128x400G FR4 机箱配置(图源:思科博客)

英特尔

在光电共封这一技术上,英特尔是资深的玩家之一。2015年宣布推出其co-package photonic技术。为了提供经济高效的互连解决方案,英特尔一直在增加其硅光子学的带宽,并在不断探索使用一体封装的光学器件。

2019年,Intel收购了以太网交换机芯片和数据中心软件领域的新兴领军企业Barefoot Networks,2020年3月,英特尔展示了12.8 Tb/s Barefoot Tofino 2交换机与1.6 Tb/s集成光子引擎共同封装的方案,硅光互连平台采用1.6 Tbps光子引擎,在Intel硅光平台上设计和制造,可提供4个400GBase-DR4 接口。英特尔表示,使用一体封装的光学器件,可将光学端口置于在同一封装内的交换机附近,从而可降低功耗,并继续保持交换机带宽的扩展能力。英特尔还表示,其51.2 Tb/s解决方案应该可以在2023年底进行商业部署,

(图源:英特尔)

CPU和GPU厂商的试炼

相信英特尔如此致力于硅光研究不是仅仅为了能与交换机新芯片共连,未来光学器件如果能否与CPU、GPU或XPU集成在一起也不得而知。

我们看到,英特尔花费了很大的心力,从多种路径进行对光互联技术的支持。2022年6月30日,英特尔研究院展示了完全集成在硅晶圆上的八波长分布式反馈(DFB),激光器阵列,该阵列输出功率均匀性达到+/- 0.25分贝(dB),波长间隔均匀性到达±6.5%,这项最新的光电共封装解决方案使用了密集波分复用(DWDM)技术,展现了在增加带宽的同时显著缩小光子芯片尺寸的前景。而且更重要的是,它是在英特尔的商用300 mm混合硅光子平台设计和制造的,因此,它为下一代光电共封装和光互连器件的量产提供了一条清晰的路径。

在2022年英特尔On峰会上,英特尔又展示了其正在开发的一项创新:在可插拔式光电共封装(pluggable co-package photonics)解决方案上的突破。英特尔的研究人员设计了一种坚固的、高良率的、玻璃材质的解决方案,它通过一个可插拔的连接器简化了制造过程,降低了成本,为未来新的系统和芯片封装架构开启了全新可能。

英特尔可插拔连接器(图源:英特尔)

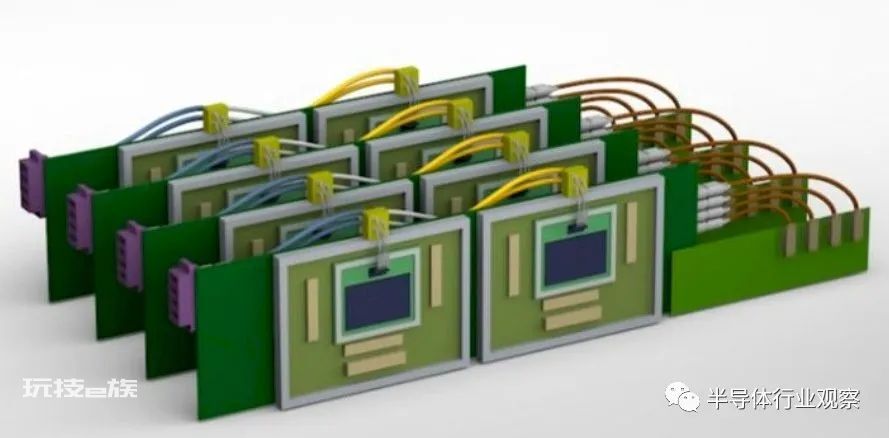

英伟达也看中了光互连的潜力,互连的 GPU 将受益于低延迟数据传输和显着减少的信号损失。Nvidia或将在下一代 NVSwitch上实施联合封装光学器件以实现节点间通信,这些系统应该在互连的NVLink 网络中支持约4,000个GPU。

英伟达展示光学链接GPU系统的外观(图源:英伟达)

英伟达正在集各方之力推动这一技术的实施。据台媒报道,业内消息人士透露,台积电参与了由Nvidia牵头的研发项目,该项目将其称为 COUPE(紧凑型通用光子引擎)的硅光子 (SiPh) 集成技术用于图形硬件,以组合多个 AI GPU。

在2023年的OFC会上,Ayar Labs展示了业界首个4太比特/秒(Tbps)双向波分复用(WDM)光学解决方案。而NVIDIA 的加速计算平台正是由WDM光学互连等先进技术支持,英伟达希望通过光互连为AI提供“下一个百万倍”加速。Nvidia还参与了Ayar Labs去年的C轮融资,当时它筹集1.3亿美元用于开发其带外激光器和硅光子互连。两家公司计划共同加速光学I/O技术的开发和采用,以支持 AI 和机器学习 (ML) 应用程序和数据量的爆炸式增长。

光电共封技术商业化还有诸多挑战

但是,光电共封技术要获得大规模的商业化还需要解决多个挑战,它必须可靠、可维修、可部署、可显著节能并且具有成本效益。虽然光互连有望让芯片间的带宽达到更高水平,特别是在数据中心内部,但制造上的困难使其成本高昂到难以承受。

挑战一,CPO技术严重依赖于硅光子学技术,需要将光学元件小型化以适应 ASIC 封装(体积比传统 QSFP-DD 或 OSFP 模块小 100 多倍)。我们看到,专有的CPO方案首先出现在Broadcom、Intel、Marvell和其他一些公司,这些供应商大多已经收购或与创新的硅光子公司合作。他们在这一技术上的积累和努力,使得CPO的商业化渐渐成为可能。

另一方面,随着光学和硅芯片的高度集成,新的工程能力和晶圆代工厂将是非常需要的。

在这方面,格芯是一个比较具有前瞻的代工厂。自从退出芯片先进制程的追逐后,格芯一直在探索其他技术,硅光子正是格芯押注大筹码的一项技术。2015 年格芯收购了IBM Microelectronics 的一部分,因此也从IBM Research 获得了光子学专业知识和知识产权。2016年,格芯就推出了其第一代硅光子平台,并在同年创建了一个独立的硅光子业务。当时带宽的行业标准是仅为40 GB/s。格芯打赌未来行业将不得不利用光的力量在全球各地涌现的数据中心内部和之间移动大量数据。事实证明,确实如此,如今数据中心的带宽已来到400 GB/s和800 GB/s的数据速率。

GF Fotonix 是格芯为硅光子芯片打造的一个整体的平台,这也是业界唯一的硅光子大批量 300mm CMOS制造代工厂。根据格芯的介绍,该平台将光子元件与高性能CMOS逻辑和RF集成在一起,以实现完全集成的单片电气和光学计算和通信引擎,同时针对低信号损耗降级进行了优化。此外,格芯单片硅光子平台的光输入和光输出可通过高密度光纤阵列、片上集成激光器和铜金属化实现与其他半导体芯片的 2.5D 和 3D 异构集成。

位于纽约马耳他的Fab8是格芯GF Fotonix芯片的生产地

芯片巨头如Broadcom、思科、Marvell和NVIDIA以及Ayar Labs、Lightmatter、PsiQuantum、Ranovus 和 Xanadu 在内的光子计算领域的厂商都与格芯有着密切的交流合作。此外,EDA软件厂商Ansys、Cadence和Synopsys等也正在提供支持基于集成硅光子学的芯片和小芯片的设计工具。

写在最后

总而言之,光电共封的解决方案确实使得新一代的交换机与前几代相比发生了很大的突破,但是如文中所述,CPO要成为主流还有诸多因素要克服,据Yole分析师的说法,尽管CPO具有技术优势,但它将很难与可插拔模块竞争,在很长一段时间内,可插拔模块仍将是首选。可插拔、OBO和CPO将共存一段时间。

图源:Yole

现在,光学器件可以与以太网交换机芯片共同封装,未来,它能否与CPU、GPU或XPU集成在一起也或许是一个探究方向。在摩尔定律动力不足的情况下,光电共封这项技术正在崭露其潜力,从另一条新道路上来满足当下数据量蓬勃发展的处理需求。而且很重要的一个趋势是,主要的芯片巨头们都在排兵布阵,光电共封技术正在向我们走进。

本文来自微信公众号“半导体行业观察”(ID:icbank),作者:杜芹DQ。